# Notes - Unit 6

## SYNCHRONOUS SEQUENTIAL CIRCUITS

## **ASYNCHRONOUS CIRCUITS: LATCHES**

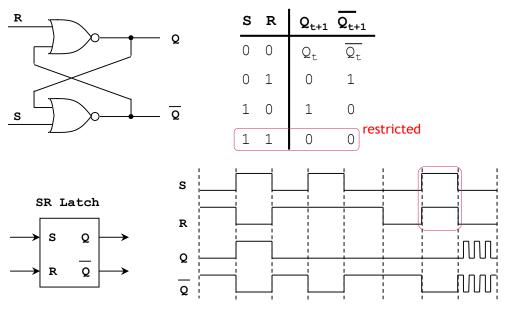

## SR LATCH:

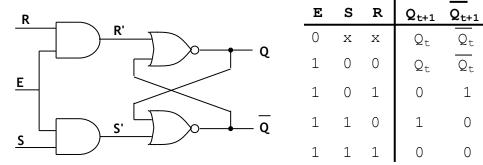

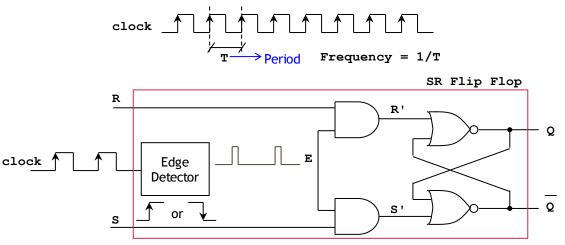

#### **SR LATCH WITH ENABLE:**

## **D LATCH WITH ENABLE:**

• This is essentially an SR Latch, where R = not(D), S = D

Qt

Qt

1

0

0

## SYNCHRONOUS CIRCUITS:

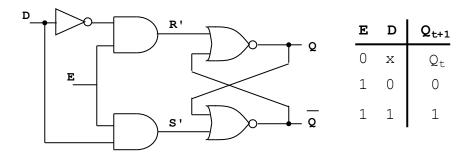

## **FLIP FLOPS**

- Flip flops are made out of:

- A Latch with an enable input.

- An Edge detector circuit.

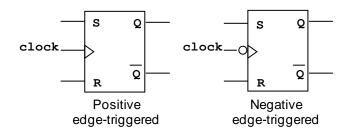

- The figure depicts an SR Latch, where the enable is connected to the output of an *Edge Detector* Circuit. The input to the Edge Detector is a signal called '*clock*'. A clock signal is a square wave with a fixed frequency.

- The edge detector circuit generates short-duration pulses during rising (or falling) edges. These pulses act as enable of the Latch.

- The behavior of the flip flops can be described as that of a Latch that is only enabled during rising (or falling edges).

- Flip flops classification:

- Positive-edge triggered flip flop: The edge detector circuit generates pulses during rising edges.

- Negative-edge triggered flip flop: The edge detector circuit generates pulses during falling edges.

#### **SR Flip Flop**

| clock | S   | R | Q <sub>t+1</sub> | $\overline{Q_{t+1}}$ |       |

|-------|-----|---|------------------|----------------------|-------|

|       | 0   | 0 | Qt               | Qt                   | S     |

|       | 0   | 1 | 0                | 1                    | clock |

|       | - 1 | 0 | 1                | 0                    | R     |

|       | - 1 | 1 | 0                | 0                    |       |

$Q_{t+1} = S\overline{R} + Q_t \overline{S}\overline{R} = \overline{R}(S + Q_t \overline{S}) = \overline{R}(S + \overline{S})(S + Q_t) = \overline{R}S + \overline{R}Q_t \text{ (on the edge)}$

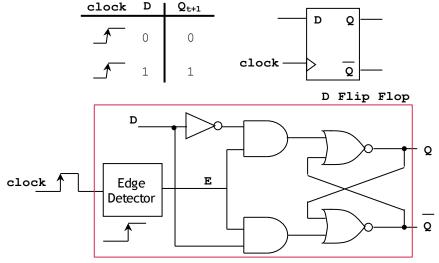

### **D** Flip Flop

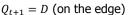

#### **T Flip Flop**

$Q_{t+1} = T \oplus Q_t$  (on the edge)

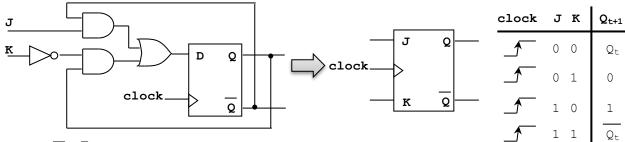

#### **JK Flip Flop**

$Q_{t+1} = J\overline{Q_t} + \overline{K}Q_t$  (on the edge)

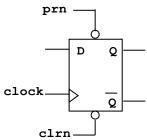

#### Synchronous/Asynchronous Inputs

- So far, the flip flops can only change their outputs on the rising (or falling edge). The outputs are usually changed due to a change in the inputs. These inputs are known as *synchronous inputs*, as the inputs' state is only checked on the rising (or falling) edges.

- However, in many instances, it is useful to have inputs that force the outputs to a value immediately, disregarding the rising (or falling edges). These inputs are known as asynchronous inputs.

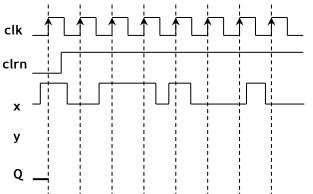

- In the example, we see a D Flip Flop with two asynchronous inputs:

- o prn: Preset (active low). When prn='0', the output q becomes 1.

- $\circ$  clrn: Clear (active low). When clrn='0', the output q becomes 0.

- If prn and clrn are both 0, usually clrn is given priority.

- A Flip flop could have more than one asynchronous inputs, or none.

## **PRACTICE EXERCISES**

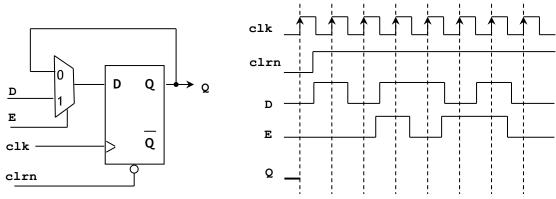

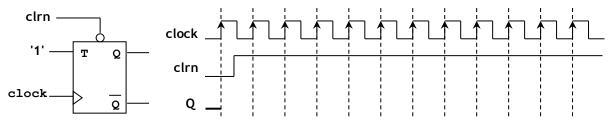

1. Complete the timing diagram of the circuit shown below:

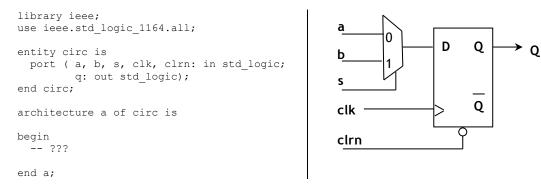

2. Complete the VHDL description of the circuit shown below:

3. Complete the timing diagram of the circuit shown below. If the frequency of the signal clock is 25 MHz, what is the frequency (in MHz) of the signal Q?

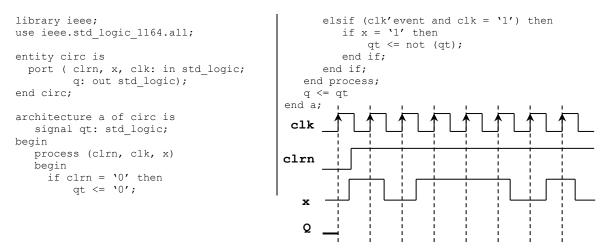

4. Complete the timing diagram of the circuit whose VHDL description is shown below:

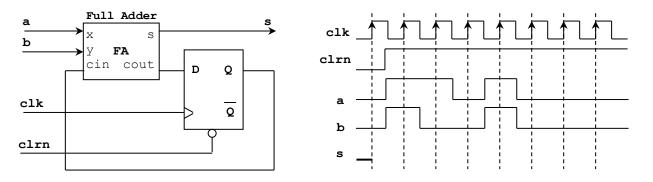

5. Complete the timing diagram of the circuit shown below:

6. Complete the VHDL description of the synchronous sequential circuit whose truth table is shown below:

| clrn | clk | A | в | Q <sub>t+1</sub> |

|------|-----|---|---|------------------|

| 1    |     | 0 | 0 | 1                |

| 1    |     | 0 | 1 | С                |

| 1    |     | 1 | 0 | Qt               |

| 1    |     | 1 | 1 | Qt               |

| 0    | Х   | Х | Х | 0                |

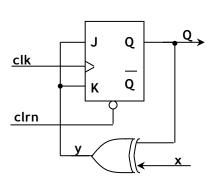

7. Complete the timing diagram of the circuit shown below:

8. Complete the timing diagram of the circuit shown below:

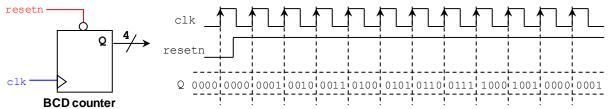

## **REGISTERS:**

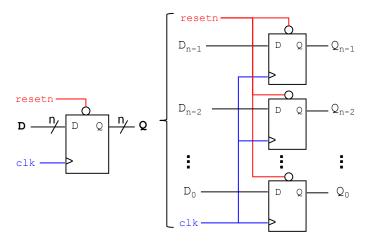

**N-BIT REGISTER:** This is a collection of 'n' D-type flip flops, where each flip flop independently stores one bit. The flip flops are connected in parallel. They also share the same resetn and clock signals.

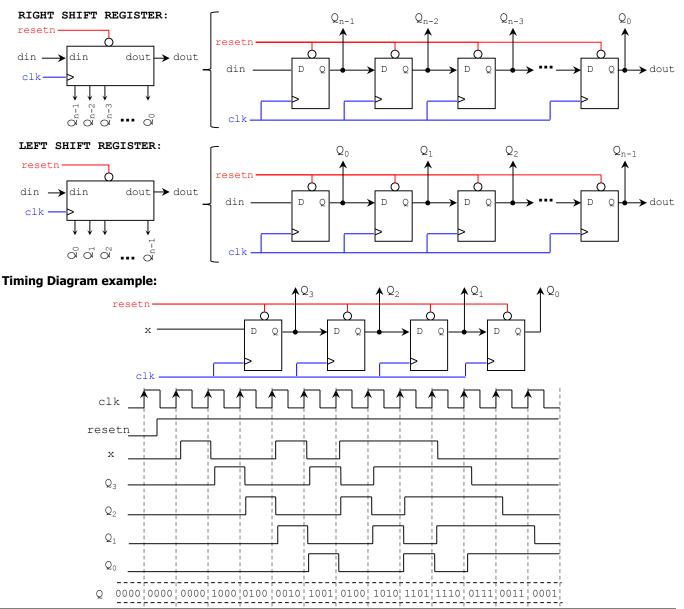

**N-BIT SHIFT REGISTER:** This is a collection of 'n' D-type flip flops, connected serially. The flip flops share the same resetn and clock signals. The serial input is called 'din', and the serial output is called 'dout'. The flip flop outputs (also called the parallel output) are called  $Q = Q_{n-1}Q_{n-2} \cdots Q_0$ . Depending on how we label the bits, we can have:

- Right shift register: The input bit moves from the MSB to the LSB, and

- Left shift register: The input bit moves from the LSB to the MSB.

6

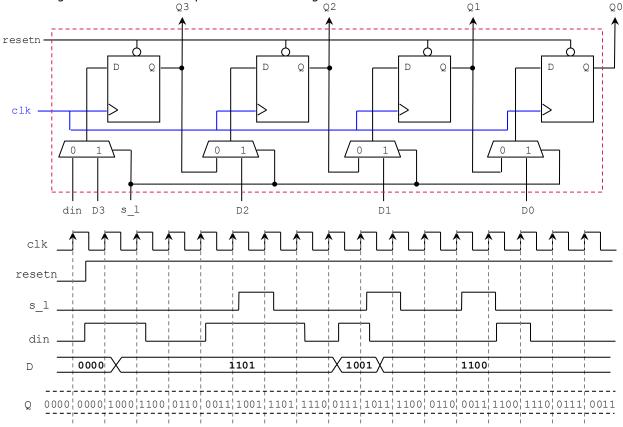

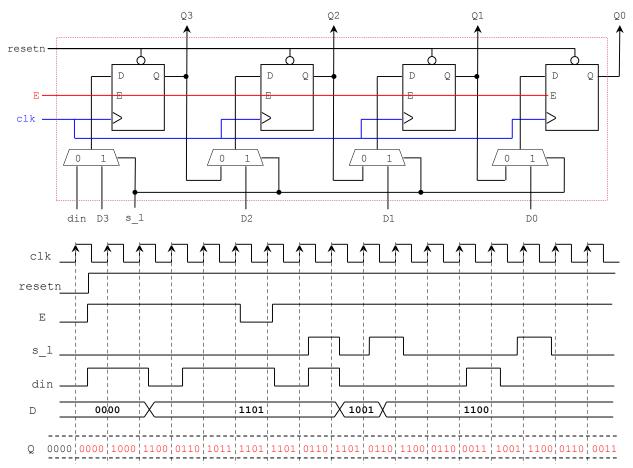

## Parallel access shift register:

• This is a shift register in which we can write data on the flip flops in parallel.  $s_l = 0 \rightarrow$  shifting operation,  $s_l = 1 \rightarrow$  parallel load. The figure below shows a 4-bit parallel access shift register.

#### Adding enable to flip flops:

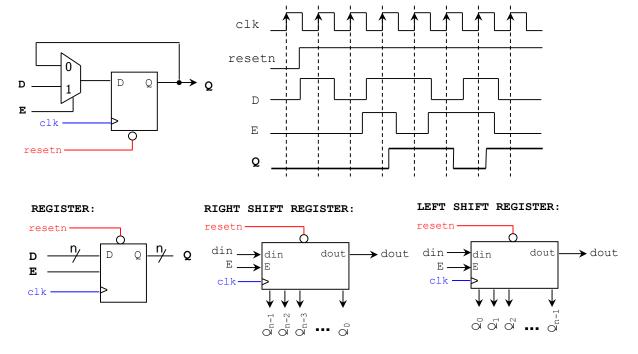

- In many instances, it is very useful to have a signal that controls whether the value of the flip flop is kept. The following circuit represent a flip flop with synchronous enable. When E = 0', the flip flop keeps its value. When E = 1', the flip flop grabs the value at the input D.

- We can thus create n-bit registers and n-bit shift registers with enable. Here, all the flip flops share the same enable input.

## Parallel access shift register with enable

• All the flip flops share the same enable input.

## SYNCHRONOUS COUNTERS

- Counters are useful for: counting the number of occurrences of a certain event, generate time intervals for task control, track elapsed time between two events, etc. Counters are made of flip flops and combinatorial logic. They are usually designed using Finite State Machines (FSM).

- Synchronous counters change their output on the clock edge (rising or falling). Each flip flop shares the same clock input signal. If the initial count is zero, each flip flop shares the resetn input signal.

#### COUNTER CLASSIFICATION:

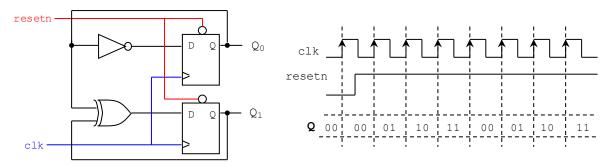

a) **Binary counter**: An n - bit counter counts from 0 to  $2^n - 1$ . The figure depicts a 2-bit counter.

b) Modulus counter: A counter modulo – N counts from 0 to N-1. Special case: BCD (or decade) counter: Counts from 0 to 9.

- c) Up/down counter: Counts both up and down, under command of a control input.

- d) Parallel load counter: The count can be given an arbitrary value.

- e) **Counter with enable**: If enable = 0, the count stops. If enable = 1, the counter counts. This is usually done by connecting the enable inputs of the flip flops to a single enable.

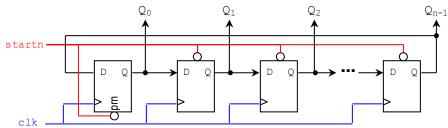

- f) **Ring counter**: Also called one-hot counter (only one bit is 1 at a time). It can be constructed using a shift register. The output of the last stage is fed back to the input to the first stage, which creates a ring-like structure. The asynchronous signal startn sets the initial count to 100...000 (first bit set to 1). Example (4-bits): 1000, 0100, 0010, 0001, 1000, ... The figure below depicts an n bit ring counter.

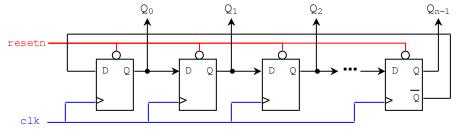

g) **Johnson counter**: Also called twisted ring counter. It can be constructed using a shift register, where the  $\bar{Q}$  output of the last flip flop is fed back to the first stage. The result is a counter where only a single bit has a different value for two consecutive counts. All the flip flops share the asynchronous signal 'resetn', which sets the initial count to 000...000. Example (4 bits): 0000, 1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000, ... The figure below depicts an n - bit Johnson counter.

## **RANDOM ACCESS MEMORY EMULATOR**

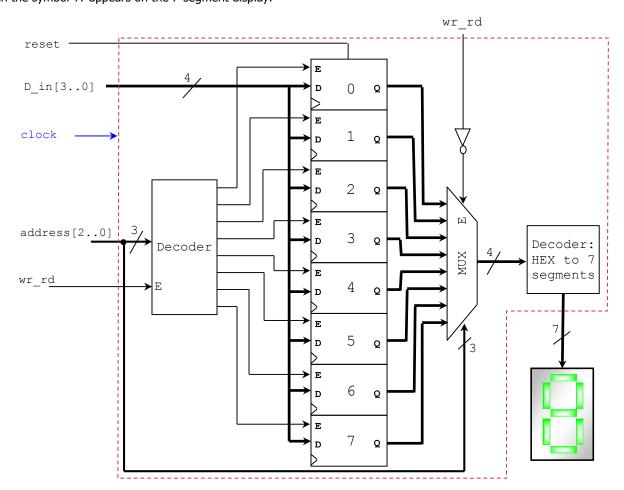

- The following sequential circuit represents a memory with 8 addresses, where each address holds a 4-bit data. The memory

positions are implemented by 4-bit registers. The reset and clock signals are shared by all the registers. Data is written or

read onto/from one of the registers (selected by the signal 'address').

- Writing onto memory (wr\_rd = 1): The 4-bit input data (D\_in) is written into one of the 8 registers. The address signal selects which register is to be written. Here, the 7-segment display must show 0. For example: if address = "101", then D\_in is written into register 5.

- Reading from memory (wr\_rd = 0): The MUX output appears on the 7-segment display (hexadecimal value). The address signal selects the register from which data is read.

For example: If address = "010", then data in register 2 must appear on the 7-segment display. If data in register 2 is '1010', then the symbol 'A' appears on the 7-segment display.

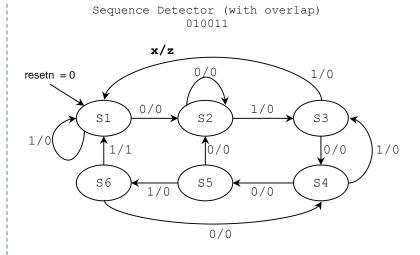

## FINITE STATE MACHINES:

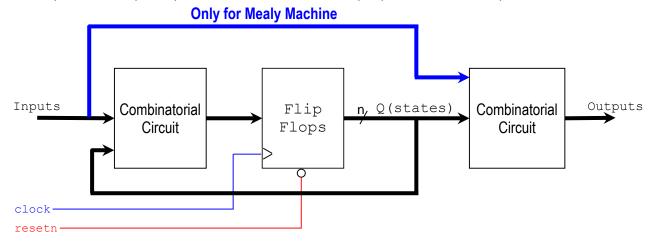

- Sequential circuits are also called Finite State Machines (FSMs), because the functional behavior of these circuits can be represented using a finite number of states (flip flop outputs).

- The signal 'resetn' sets the flip flops to an initial state.

- Classification:

- Moore machine: Outputs depend solely on the current state of the flip flops.

- Mealy machine: Outputs depend on the current state of the flip flops as well as on the input to the circuit.

- Any general sequential circuit can be represented by the figure above (Finite State Machine model).

- A sequential circuit with certain behavior and/or specification can be formally designed using the Finite State Machine method: drawing a State Diagram and coming up the Excitation Table.

- Designing sequential circuits using the Finite State Machine method is a powerful in Digital Logic Design.

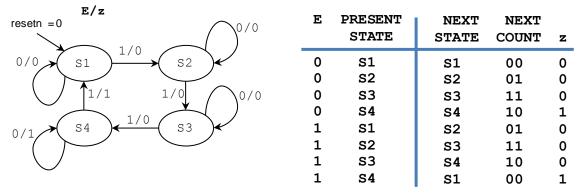

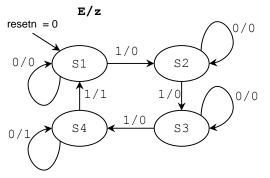

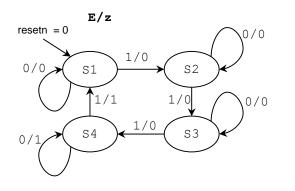

**Example**: 2-bit gray-code counter with enable and 'z' output: 00, 01, 11, 10, 00, ... The output 'z' is 1 when the present count is '10'. The count is the same as the states encoded in binary.

• *First step*: Draw the State Diagram and State Table. If we were to implement the state machine in VHDL, this is the only step we need.

- Second step: State Assignment. We assign unique flip flop states to our state labels (S1, S2, S3, S4). Notice that this is

arbitrary. However, we can save resources if we assign each state to the count that we desire. Then, the output 'count' is

just the flip flops' outputs.

- ✓ S1: Q = 00

- ✓ S2: Q = 01

- ✓ S3: Q = 11

- ✓ S4: Q = 10

• *Third step*: Excitation table. Here, we replace the state labels by the flip flop states:

|   | PRESEN             | <b>STATE</b>       | NEXTS                | NEXTSTATE  |   |  |

|---|--------------------|--------------------|----------------------|------------|---|--|

| E | Q <sub>1</sub> (t) | Q <sub>0</sub> (t) | Q <sub>1</sub> (t+1) | $Q_0(t+1)$ | z |  |

| 0 | 0                  | 0                  | 0                    | 0          | 0 |  |

| 0 | 0                  | 1                  | 0                    | 1          | 0 |  |

| 0 | 1                  | 1                  | 1                    | 1          | 0 |  |

| 0 | 1                  | 0                  | 1                    | 0          | 1 |  |

| 1 | 0                  | 0                  | 0                    | 1          | 0 |  |

| 1 | 0                  | 1                  | 1                    | 1          | 0 |  |

| 1 | 1                  | 1                  | 1                    | 0          | 0 |  |

| 1 | 1                  | 0                  | 0                    | 0          | 1 |  |

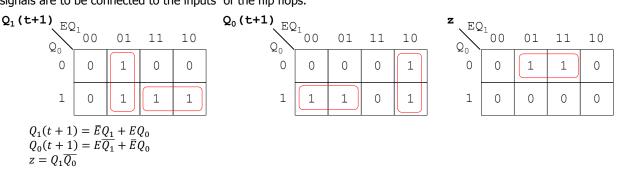

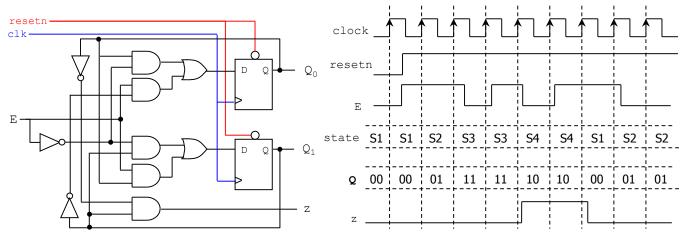

• *Fourth step*: Excitation equations and minimization.  $Q_1(t + 1)$  and  $Q_0(t + 1)$  are the next state of the flip flops, i.e. these signals are to be connected to the inputs of the flip flops.

• *Fifth step:* Circuit implementation:

**Example**: 2-bit counter with enable and 'z' output. The output 'z' is 1 when the present count is '11'. The count is the same as the states encoded in binary.

First step: Draw the State Diagram and State Table. If we were to implement the state machine in VHDL, this is the only step we need.

| E | PRESENT<br>STATE | NEXT<br>STATE | NEXT<br>COUNT | z |

|---|------------------|---------------|---------------|---|

| 0 | S1               | S1            | 00            | 0 |

| 0 | S2               | S2            | 01            | 0 |

| 0 | S3               | S3            | 10            | 0 |

| 0 | S4               | S4            | 11            | 1 |

| 1 | S1               | S2            | 01            | 0 |

| 1 | S2               | <b>S</b> 3    | 10            | 0 |

| 1 | S3               | S4            | 11            | 0 |

| 1 | S4               | S1            | 00            | 1 |

- Second step: State Assignment. We assign unique flip flop states to our state labels (S1, S2, S3, S4). Notice that this is

arbitrary. However, we can save resources if we assign each state to the count that we desire. Then, the output 'count' is

just the flip flops' outputs.

- ✓ S1: Q = 00 ✓ S2: Q = 01 ✓ S3: O = 10

- ✓ S3: Q = 10

✓ S4: Q = 11

- *Third step*: Excitation table. Here, we replace the state labels by the flip flop states:

|   | PRESEN             |          | NEXTS                |                      |   |

|---|--------------------|----------|----------------------|----------------------|---|

| Е | Q <sub>1</sub> (t) | $Q_0(t)$ | Q <sub>1</sub> (t+1) | Q <sub>0</sub> (t+1) | z |

| 0 | 0                  | 0        | 0                    | 0                    | 0 |

| 0 | 0                  | 1        | 0                    | 1                    | 0 |

| 0 | 1                  | 0        | 1                    | 0                    | 0 |

| 0 | 1                  | 1        | 1                    | 1                    | 1 |

| 1 | 0                  | 0        | 0                    | 1                    | 0 |

| 1 | 0                  | 1        | 1                    | 0                    | 0 |

| 1 | 1                  | 0        | 1                    | 1                    | 0 |

| 1 | 1                  | 1        | 0                    | 0                    | 1 |

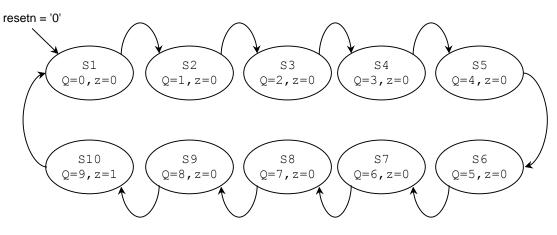

**Example**: BCD counter. Output 'z' becomes '1' when the count is 1001.

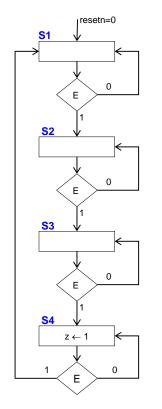

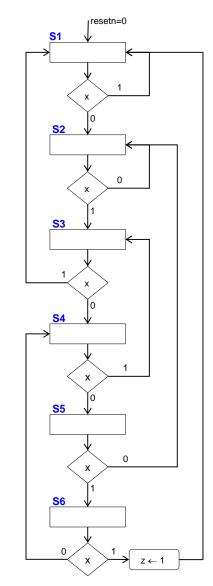

# ALGORITHMIC STATE MACHINE (ASM) CHARTS:

Gray counter, z=1 when Q=10

## Modifying the rate of change of a Finite State Machine:

- We usually would like to reduce the rate at which FSM transitions occur. A straightforward option is to reduce the frequency of the input clock. But this is a very complicated problem when a high precision clock is required.

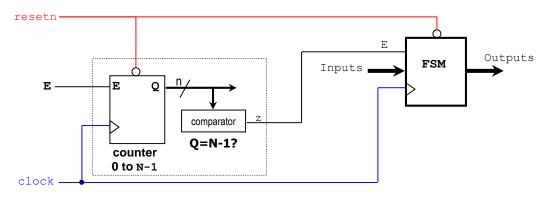

- Alternatively, we can reduce the rate at which FSM transitions occur by including an enable signal in our FSM: this means

including an enable to every flip flop in the FSM. For any FSM transition to occur, the enable signal has to be '1'. Then we

assert the enable signal only when we need it. The effect is the same as reducing the frequency of the input clock.

- ✓ The figure below depicts a counter modulo-N (from 0 to N-1) connected to a comparator that generates a pulse (output signal 'z') of one clock period every time we hit the count 'N-1'. The number of bits the counter is given by  $n = \lceil \log_2 N \rceil$ . The effect is the same as reducing the frequency of the FSM to f/N, where f is the frequency of the clock.

- ✓ A modulo-N counter is better designed using VHDL behavioral description, where the count is increased by 1 every clock cycle and 'z' is generated by comparing the count to 'N-1'. A modulo-N counter could be designed by the State Machine method, but this can be very cumbersome if N is a large number. For example, if N = 1000, we need 1000 states.

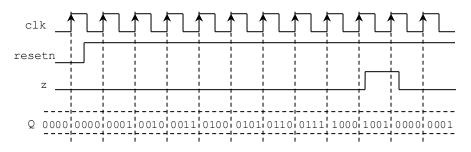

✓ As an example, we provide the timing diagram of the counter from 0 to N-1, when N=10. Notice that 'z' is only activated when the count reaches "1001". This 'z' signal controls the enable of a state machine, so that the FSM transitions only occur every 10 clock cycles, thereby having the same effect as reducing the frequency by 10.

• We can apply the same technique not only to FSMs, but also to any sequential circuit. This way, we can reduce the rate of any sequential circuit by including an enable signal of every flip flop in the circuit.